# Moving Forward with OpenMP\* Implementation in LLVM and Clang

Xinmin Tian, Alexey Bataev, Andrey S. Bokhanko, James H. Cownie, Ayal Zaks Intel Corporation November 15th, 2015

SC'2015 LLVM-HPC2 Workshop

#### Legal Notice and Disclaimers

By using this document, in addition to any agreements you have with Intel, you accept the terms set forth below.

You may not use or facilitate the use of this document in connection with any infringement or other legal analysis concerning Intel products described herein. You agree to grant Intel a non-exclusive, royalty-free license to any patent claim thereafter drafted which includes subject matter disclosed herein.

INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL PRODUCTS. NO LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. EXCEPT AS PROVIDED IN INTEL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, INTEL ASSUMES NO LIABILITY WHATSOEVER AND INTEL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY, RELATING TO SALE AND/OR USE OF INTEL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

A "Mission Critical Application" is any application in which failure of the Intel Product could result, directly or indirectly, in personal injury or death. SHOULD YOU PURCHASE OR USE INTEL'S PRODUCTS FOR ANY SUCH MISSION CRITICAL APPLICATION, YOU SHALL INDEMNIFY AND HOLD INTEL AND ITS SUBSIDIARIES, SUBCONTRACTORS AND AFFILIATES, AND THE DIRECTORS, OFFICERS, AND EMPLOYEES OF EACH, HARMLESS AGAINST ALL CLAIMS COSTS, DAMAGES, AND EXPENSES AND REASONABLE ATTORNEYS' FEES ARISING OUT OF, DIRECTLY, OR INDIRECTLY, ANY CLAIM OF PRODUCT LIABILITY, PERSONAL INJURY, OR DEATH ARISING IN ANY WAY OUT OF SUCH MISSION CRITICAL APPLICATION, WHETHER OR NOT INTEL OR ITS SUBCONTRACTOR WAS NEGLIGENT IN THE DESIGN, MANUFACTURE, OR WARNING OF THE INTEL PRODUCT OR ANY OF ITS PARTS.

Intel may make changes to specifications and product descriptions at any time, without notice. Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined". Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them. The information here is subject to change without notice. Do not finalize a design with this information.

The products described in this document may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an order number and are referenced in this document, or other Intel literature, may be obtained by calling 1-800-548-4725, or go to: http://www.intel.com/design/literature.htm

Software and workloads used in performance tests may have been optimized for performance only on Intel microprocessors. Performance tests, such as SYSmark and MobileMark, are measured using specific computer systems, components, software, operations and functions. Any change to any of those factors may cause the results to vary. You should consult other information and performance tests to assist you in fully evaluating your contemplated purchases, including the performance of that product when combined with other products.

#### For more complete information about performance and benchmark results, visit Performance Test Disclosure

Intel does not control or audit the design or implementation of third party benchmark data or Web sites referenced in this document. Intel encourages all of its customers to visit the referenced Web sites or others where similar performance benchmark data are reported and confirm whether the referenced benchmark data are accurate and reflect performance of systems available for purchase. Intel processor numbers are not a measure of performance.

Processor numbers differentiate features within each processor family, not across different processor families: Go to: Learn About Intel® Processor Numbers

Intel<sup>®</sup> Advanced Vector Extensions (Intel<sup>®</sup> AVX)<sup>\*</sup> are designed to achieve higher throughput to certain integer and floating point operations. Due to varying processor power characteristics, utilizing AVX instructions may cause a) some parts to operate at less than the rated frequency and b) some parts with Intel<sup>®</sup> Turbo Boost Technology 2.0 to not achieve any or maximum turbo frequencies. Performance varies depending on hardware, software, and system configuration and you should consult your system manufacturer for more information.

\*Intel® Advanced Vector Extensions refers to Intel® AVX, Intel® AVX2 or Intel® AVX-512. For more information on Intel® Turbo Boost Technology 2.0, visit http://www.intel.com/go/turbo

#### **Optimization Notice**

Intel's compilers may or may not optimize to the same degree for non-Intel microprocessors for optimizations that are not unique to Intel microprocessors. These optimizations include SSE2, SSE3, and SSSE3 instruction sets and other optimizations. Intel does not guarantee the availability, functionality, or effectiveness of any optimization on microprocessors not manufactured by Intel. Microprocessor-dependent optimizations in this product are intended for use with Intel microprocessors. Certain optimizations not specific to Intel microarchitecture are reserved for Intel microprocessors. Please refer to the applicable product User and Reference Guides for more information regarding the specific instruction sets covered by this notice.

#### Notice revision #20110804

Copyright © 2014 Intel Corporation. All rights reserved . Intel, the Intel logo, Intel Xeon, and Intel Xeon Phi are trademarks of Intel Corporation in the U.S. and/or other countries. \*Other names and brands may be claimed as property of others.

Copyright © 2014, Intel Corporation. All rights reserved. \*Other names and brands may be claimed as the property of others.

### Agenda

OpenMP\* Programming Model's New Era

Programming Model Overview

OpenMP\* Support in Clang/LLVM: A Brief History

10000ft View: A High-Level Design for Moving Forward

- ✓ Design Guidelines

- ✓ Back-End: LLVM Prepass, Lowering and Outlining

✓ An Example

OpenMP\* SIMD extension support in LLVM

✓ Declare SIMD support

Copyright © 2014, Intel Corporation. All rights reserved. \*Other names and brands may be clair

$\checkmark$  Vectorizng Loops with math function calls

Summary

### What is OpenMP?

- ✓ De-facto standard Application Programming Interface (API) to write <u>shared</u> <u>memory parallel</u> applications in C, C++, and Fortran

- ✓ Consists of Compiler Directives, Runtime routines and Environment variables

- Specification maintained by the OpenMP Architecture Review Board (<u>http://www.openmp.org</u>)

- ✓ New ARB mission statement:

- ✓ "The OpenMP ARB mission is to standardize directive-based multi-language highlevel parallelism that is performant, productive and portable."

- ✓ OpenMP\* Specification Version 4.5 was launched in Now at SC'2015

### OpenMP\* Programming Model's New Era

- ✓ CPUs and All forms of accelerators/coprocessors, GPU, APU, GPGPU, FPGA, and DSP

- ✓ Heterogenous consumer devices

- ✓ Kitchen appliances, drones, signal processors, medical imaging, auto, telecom, automation, not just graphics engines – (Courtesy of Michael Wong (IBM) and Alexey Bataev (intel), et.al. LLVM Developer Conference Oct. 2105)

© 2014. Intel Corporation. All rights reserved. \*Other names and brands may be claimed as the property of o

| Search OpenMP.org                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Members                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|

| Google" Custom Search<br>Search<br>Archives<br>• June 2014<br>• April 2014<br>• March 2014<br>• February 2014<br>• January 2014<br>• December 2013<br>• November 2013<br>• November 2013<br>• September 2013<br>• July 2013<br>• May 2013<br>• May 2013<br>• April 2013<br>• March 2013<br>• February 2013<br>• January 2013<br>• January 2013<br>• December 2012<br>• November 2012<br>• November 2012<br>• October 2012<br>• September 2012<br>• July 2012<br>• June 2012<br>• June 2012<br>• March 2012<br>• March 2012<br>• June 2012<br>• June 2012<br>• March 2012<br>• March 2012<br>• March 2012<br>• June 2012<br>• March 2012<br>• Mar | Permanent Members of the ARB:         • AMD (Dibyendu Das)         • Convey Computer (Kirby Collins)         • Cray (James Beyer/Luiz DeRose)         • Fujitsu (Eiji Yamanaka)         • HP (Sujoy Saraswati)         • IBM (Kelvin Li)         • Intel (Xinmin Tian)         • NEC (Kazuhiro Kusano)         • NVIDIA (Jeff Larkin)         • Oracle Corporation (Nawal Copty)         • Red Hat (Matt Newsome)         • ST Microelectronics (Christian Bertin         • Texas Instruments (Andy Fritsch)         Auxiliary Members of the ARB:         • ANL (Kalyan Kumaran)         • ASC/LLNL (Bronis R. de Supinski)         • BSC (Xavier Martorell)         • COMPunity (Barbara Chapman)         • EPCC (Mark Bull)         • LANL (David Montoya)         • NASA (Henry Jin)         • ORNL (Oscar Hernandez)         • RWTH Aachen University (Dieter and SNL-Sandia National Lab (Steven Olif         • Texas Advanced Computing Center         • University of Houston (Yonghong Yar) | Mey)<br>ver)<br>(Kent Milfeld) |

Copyright © 2014, Intel Corporation. All rights reserved. \*Other names and brands may be claimed as the property of others.

openmp.org/wp/about-openmp/

Optimization Notice

☆ マ C 🛛 🔁 - Google

P 🖸 -

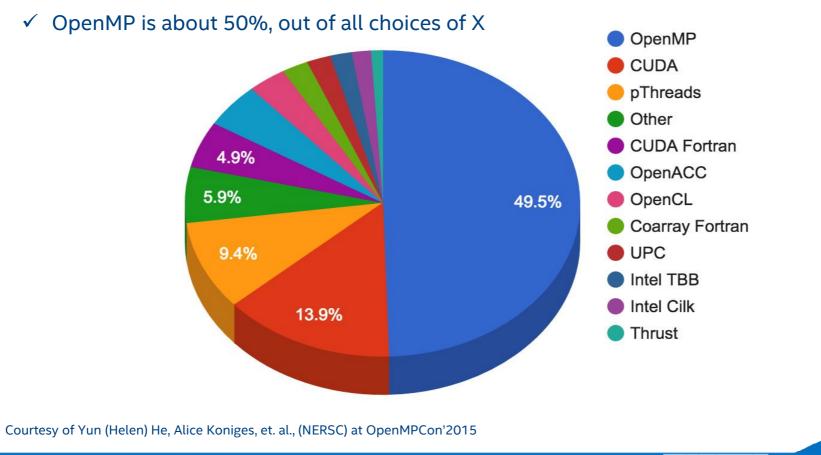

#### Programming Models Used at NERSC

#### ✓ MPI dominates

#### ✓ 40% of projects use OpenMP\*

#### Programming Models Used at NERSC 2015

(Taken from allocation request form. Sums to >100% because codes use multiple languages)

### What is X if Use MPI+X at NERSC

(intel) **Optimization Notice** Copyright © 2014, Intel Corporation. All rights reserved. \*Other names and brands may be claimed as the property of others

# Parallel + SIMD is the Path Forward

Intel® Xeon® and Intel® Xeon Phi™ Product Families are both going parallel

|            | Intel <sup>®</sup> Xeon <sup>®</sup><br>processor<br>64-bit | Intel <sup>®</sup> Xeon <sup>®</sup><br>processor<br>5100<br>series | Intel <sup>®</sup> Xeon <sup>®</sup><br>processor<br>5500<br>series | Intel <sup>®</sup> Xeon <sup>®</sup><br>processor<br>5600<br>series | Intel <sup>®</sup> Xeon <sup>®</sup><br>processor<br>code-named<br>Sandy<br>Bridge EP | Intel <sup>®</sup> Xeon <sup>®</sup><br>processor<br>code-named<br>Ivy Bridge<br>EP | Intel <sup>®</sup> Xeon <sup>®</sup><br>processor<br>code-named<br>Haswell<br>EP | Intel® Xeon<br>Processor<br>codenamed<br>Skylake<br>EP | Intel" Xeon Phi™<br>coprocessor<br>Knights<br>Corner | Intel <sup>®</sup> Xeon Phi™<br>processor &<br>coprocessor<br>Knights<br>Landing <sup>1</sup> |

|------------|-------------------------------------------------------------|---------------------------------------------------------------------|---------------------------------------------------------------------|---------------------------------------------------------------------|---------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|--------------------------------------------------------|------------------------------------------------------|-----------------------------------------------------------------------------------------------|

| Core(s)    | 1                                                           | 2                                                                   | 4                                                                   | 6                                                                   | 8                                                                                     | 12                                                                                  | 18                                                                               | 28                                                     | 61                                                   | 70+                                                                                           |

| Threads    | 2                                                           | 2                                                                   | 8                                                                   | 12                                                                  | 16                                                                                    | 24                                                                                  | 36                                                                               | 56                                                     | 244                                                  | 280+                                                                                          |

| SIMD Width | 128                                                         | 128                                                                 | 128                                                                 | 128                                                                 | 256                                                                                   | 256                                                                                 | 256                                                                              | 512                                                    | 512                                                  | 512                                                                                           |

More cores → More Threads → Wider vectors OpenMP\* is one of most important vehicles for the parallel + SIMD path forward

\*Product specification for launched and shipped products available on ark.intel.com. 1. Not launched or in planning.

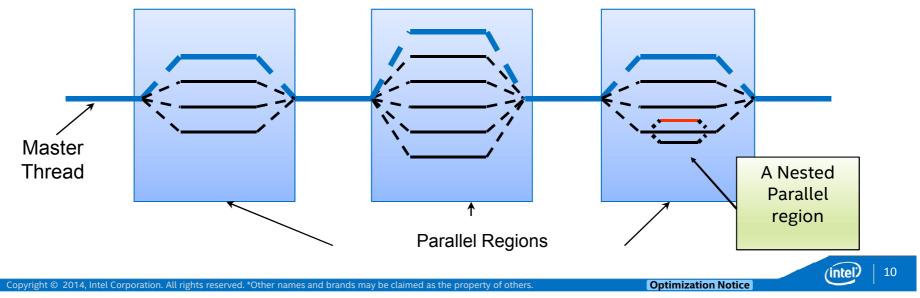

#### OpenMP\* Programming Model

- Master thread spawns a team of threads / a league of thread teams as needed.

- Parallelism is added incrementally until desired performance is achieved: i.e. the sequential program evolves into a parallel program.

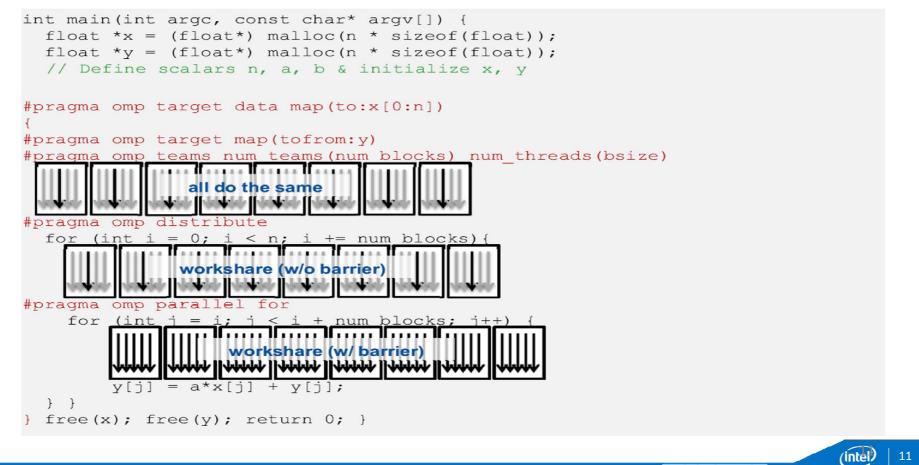

#### SAXPY: Coprocessor/Accelerator

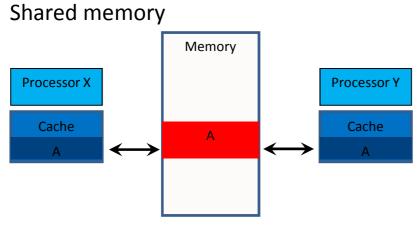

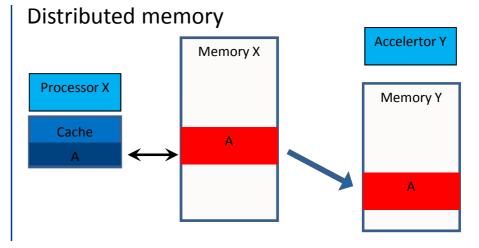

# Data sharing / mapping: shared or distributed memory

#### Threads have access to a shared memory

- for **shared** data

- each thread can have a temporary view of the shared memory (e.g. registers, cache, etc.) between synchronization barriers.

#### Threads have private memory

- for **private** data

- Each thread has a stack for data local to each task it executes

Copyright © 2014. Intel Corporation, All rights reserved, \*Other names and brands may be claimed as the property of other

- The corresponding variable in the device data environment may share storage with the original variable

- Writes to the corresponding variable may alter the value of the original variable

(intel)

12

### OpenMP\* in Clang/LLVM: A Brief History

- 2H 2012: Several proposals with LLVM IR extensions and late outlining

- $\checkmark$  From Intel, Hal Finkel, others

- $\checkmark$  All of them involve changes to LLVM IR and thus, require modifications of LLVM phases

- $\checkmark$  None of them got enough support in the community

- October 2012: OpenMP\* in Clang project

- ✓ Started by AMD<sup>\*</sup>, continued by Intel

- $\checkmark$  Early FE lowering and outlining

- ✓ OpenMP RTL calls generated in Clang

- October 2015: OpenMP\* 4.0 Target (Device) model supported in Clang FE

- ✓ Initial implementation available at <u>https://github.com/clang-omp/clang\_trunk</u>

(Joint work by AMD, IBM, Intel and TI)

\* Other brands and names are the property of their respective owners.

(intel)

13

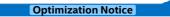

### 10000ft View: High-Level Design for Moving Forward

## LLVM OpenMP\* Compiler Design Guideline

- Correctness: easy to achieve and maintain compiler intermediate states and consistency

- Competitive performance: compile-time and runtime performance

- Competitive code size: generated code size and adds-on module size from Intel implementation.

- Composite ability: analysis module and individual loop opts can composed flexibility to achieve high performance

- ✓ Debug ability: generate sufficient debug information

- Programmer friendly diagnostic and report messages

### LLVM IR Intrinsic Definitions

Array section is represented with (2 + # of DIMs x 3) arguments: Value, # of DIMs, lower0, length0, stride0, lower1, length1, stride1, ...

Copyright © 2014, Intel Corporation. All rights reserved. \*Other names and brands may be claimed as the property of others.

(intel)

16

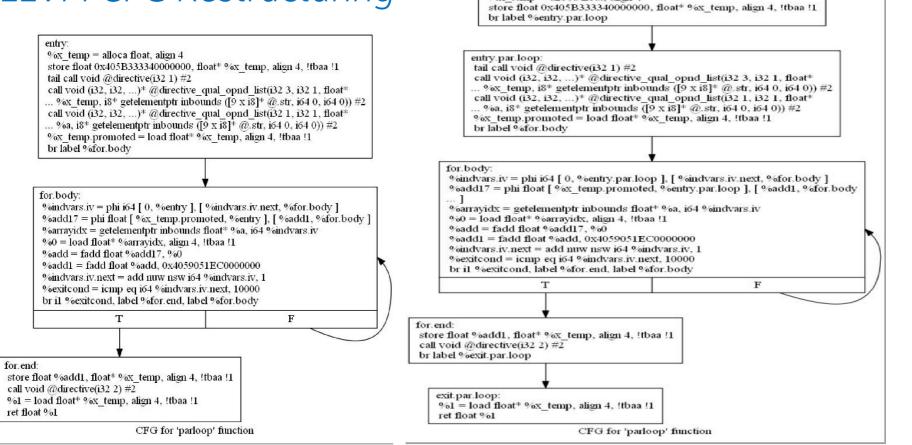

| LLVM IR Prepass                                                                                                          | float parloop(float *a) {<br>int $k = 0$ ;<br>float x = 108.8f;                                                                                  |

|--------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| ✓ CFG Restructuring                                                                                                      | <pre>#pragma omp parallel for simd reduction(+: x) shared(a) private(k) for (k=0; k&lt;10000; k++) {     x = x + a[k] + 100.08f;</pre>           |

| <ul> <li>Transform parallel sections /<br/>worksharing sections to<br/>parallel loops / worksharing<br/>loops</li> </ul> | <pre>float parloop(float *a) {     int k = 0;     float x = 108.8f;     float x temp = x;</pre>                                                  |

| ✓ Pre-privatization renaming                                                                                             | @llvm.directive(DIR.OMP.PARALLEL.LOOP);<br>@llvm.directive.qual(DIR.QUAL.IS.OMP.SIMD);<br>@llvm.directive.qual.opnd.list(DIR.QUAL.REDUCTION.ADD, |

| <ul> <li>Multi-versioning for different targets (Host, GPU and</li> </ul>                                                | DIR.QUAL.OPND.VALUE, <b>&amp;x_temp</b> );<br>@directive_qual_opnd_list(DIR_QUAL_SHARED,<br>DIR_QUAL_OPND_VALUE, a, "opnd.end");                 |

| Coprocessors)                                                                                                            | <pre>{ int priv_k; //#pragma omp parallel for simd reduction(+: x) shared(a)   for (priv_k=0; priv_k&lt;10000; priv_k++) {</pre>                 |

| ¥                                                                                                                        | <pre>x_temp = x_temp + a[priv_k] + 100.08f; } @llvm.directive(DIR.OMP.END.PARALLEL.LOOP); x = x_temp; return x;</pre>                            |

| Convisiont @ 2014 Intel Corporation All rights reserved *Other name                                                      | }                                                                                                                                                |

Copyright © 2014, Intel Corporation. All rights reserved. \*Other names and brands may be claimed as the property of others.

### LLVM IR with Directive Intrinsics

```

@.str = private unnamed addr constant [9 x i8] c"opnd.end\00", align 1

: Function Attrs: nounwind uwtable

define float @parloop(float* %a) #0 {

entry:

%x temp = alloca float, align 4

store float 0x405B33334000000, float* %x temp, align 4, !tbaa !1

call void @directive(i32 1) #2

call void @directive.gual(i32 28) #2

call void (i32, i32, ...)* @directive.gual.opndlist(i32 3, i32 1, float* %x temp, i8* getelementptr inbounds ([9 x i8]* @.str, i64 0, i64 0)) #2

call void (i32, i32, ...)* @directive.qual.opndlist(i32 1, i32 1, float* %a, i8* getelementptr inbounds ([9 x i8]* @.str, i64 0, i64 0)) #2

%x temp.promoted = load float* %x temp, align 4, !tbaa !1

br label %for.body

for.body:

; preds = %for.body, %entry

%indvars.iv = phi i64 [ 0, %entry ], [ %indvars.iv.next, %for.body ]

%add17 = phi float [ %x temp.promoted, %entry ], [ %add1, %for.body ]

%arrayidx = getelementptr inbounds float* %a, i64 %indvars.iv

%0 = load float* %arrayidx, align 4, !tbaa !1

%add = fadd float %add17, %0

%add1 = fadd float %add. 0x4059051EC0000000

%indvars.iv.next = add nuw nsw i64 %indvars.iv. 1

%exitcond = icmp eq i64 %indvars.iv.next, 10000

br i1 %exitcond, label %for.end, label %for.body

for.end:

; preds = %for.body

store float %add1, float* %x temp, align 4, !tbaa !1

call void @directive(i32 2) #2

%1 = load float* %x temp, align 4, !tbaa !1

ret float %1

```

}

Copyright © 2014, Intel Corporation. All rights reserved. \*Other names and brands may be claimed as the property of others.

**Optimization Notice**

(intel)

18

#### LLVM CFG Restructuring

entry:

%x temp = alloca float, align 4

Copyright © 2014, Intel Corporation. All rights reserved. \*Other names and brands may be claimed as the property of others.

Optimization Notice

(intel)

19

## LLVM IR Lowering and Outlining Passes

#### Lowering

- Loop transformation (e.g. loop collapsing)

- ✓ Generate code for atomic, critical, single, master, ..., constructs (i.e. these constructs do not need outlining)

- Loop partitioning based on schedule type and chunk-size

- ✓ Generation code for reduction, lastprivate, firstprivate, copyprivate, ... threadprivate, etc.

- ✓ Generate debug info and opt-reports

ohts reserved \*Other names and brands

#### Outlining

Intel Confidential

- Parallel regions/loops/sections/Tasks (use OpenMP runtime)

- ✓ Affinity setting

- ✓ Generate runtime control code

- ✓ Target regions (use Offload runtime)

- ✓ Cilk for loops (use Cilk runtime)

- ✓ Packing / Unpacking arguments

- ✓ Generate debug info and opt-reports

### Debugging Support

- ✓ Associate "privatized" LLVM VALUEs (variables) to original LLVM VALUEs (variables)

- ✓ Associate "argument" VALUEs of outlined function to original VALUEs

- ✓ LLVM debug info generation framework has similar functionalities for preserving debug info for privatization and data-sharing transformation.

# A Lowering and Outlining Example (Pseudo Code)

```

typedef struct { float *x; float *a; } PARMLIST;

float parloop(float *a) {

float x = 108.8f;

void outlined parloop(

PARMLIST thunk;

int g lower, int g upper, int g stride, PARMLIST *parms) {

int x reduction; float *a; float *x;

float x temp = x;

int t0 = 0, lower = 0, t1 = 0, upper = 0, stride = 1;

int tid = __kmpc_global_get_thread_num();

thunk.x = &x temp;

a = parms -> a; x = parms -> x;

kmpc static init(tid, &lower, &upper,

thunk.a = a;

&stride, g_lower, g_upper, g_stride);

x red = 0.0f; t0 = lower; t1 = upper;

if ( kmpc ok fork()) {

@llvm.directive(DIR.OMP.SIMD);

__kmpc_fork_call(outlined_parloop, 0, 10000, 1, &thunk);

@llvm. directive.qual.opndlist(DIR.QUAL.REDUCTION.ADD,

DIR.QUAL.OPND.VALUE, &x_red);

else {

for (int k=t0; k<t1; k++) {

outlined parloop(0, 10000, 1, &thunk);

x red = x red + a[k] + 100.8f;

}

x = x_temp;

@llvm.directive(DIR.OMP.END.SIMD);

return x;

kmpc critical(tid);

}

*x = *x + x red;

kmpc end critical(tid);

return;

}

```

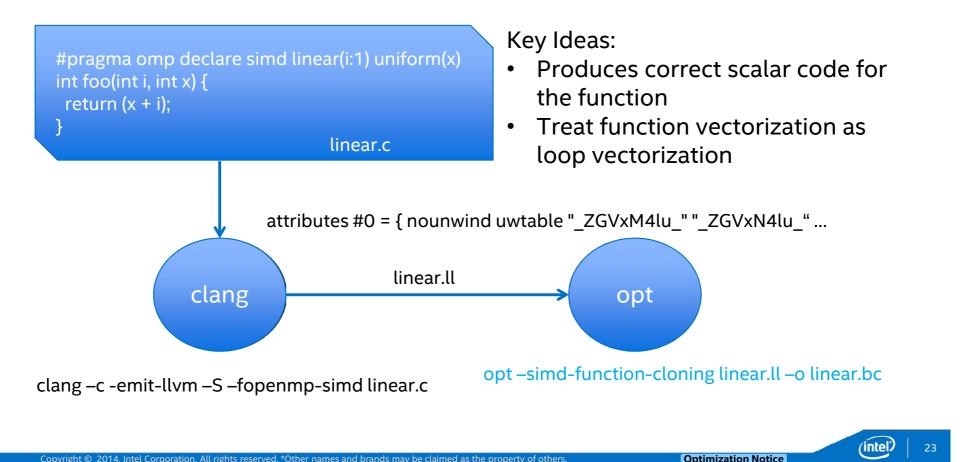

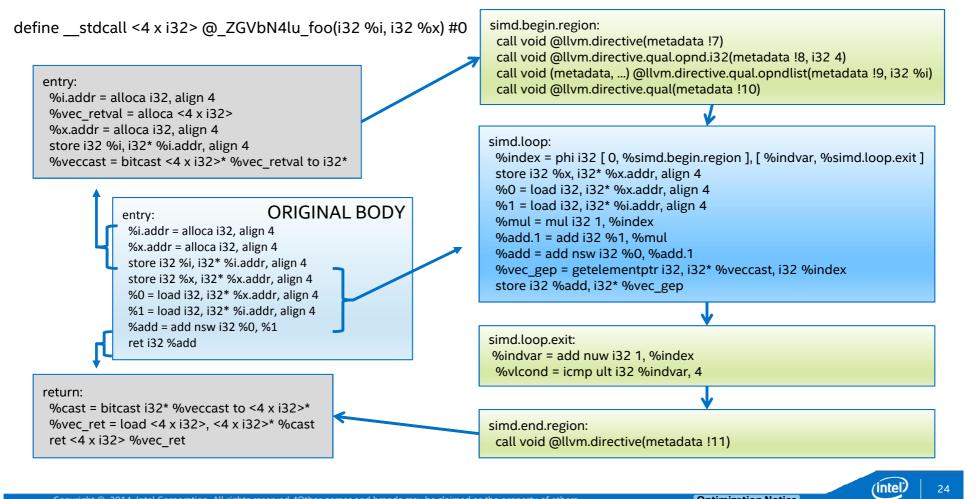

#### DECLARED SIMD: Function to Loop Conversion

Copyright © 2014, Intel Corporation. All rights reserved. \*Other names and brands may be claimed as the property of others

## Vectorizing for Loop with Math Function Calls

icc sinf.c -fimf-max-error=0.6 -fimf-precision=high

```

#pragma omp simd

for ( i = 0; i < 1000; i++) {

array[i] = sinf(i);

}</pre>

```

#### Before Vectorization:

((F32) t0(F32)) = sinf{ic=SINF}.imf\_attrs(max-error=0.6 domain-exclusion=0 valid-status-bits=false precision=high)( (F32) (EXPR\_CONV.SI32.F32(i.219\_V\$3(SI32)))(F32)); [CALL\_CONVENTION\_UNIX\_ABI]

#### After Vectorization:

((MS128) t107(MS128)) = \_\_svml\_sinf4{ic=VX\_VMLS\_SIN4}.imf\_attrs(max-error=0.6 domain-exclusion=0 valid-status-bits=false precision=high)((MS128) t108(MS128)); [CALL\_CONVENTION\_UNIX\_ABI]

| Assembly:                    |                 |       |                                          |  |  |

|------------------------------|-----------------|-------|------------------------------------------|--|--|

| B1.2:                        | # PredsB1.8B1.7 |       |                                          |  |  |

| # Execution count [5.56e+00] |                 |       |                                          |  |  |

| cvtdq2ps %                   | 6xmm8, %xmm0    | #30   | 5.3                                      |  |  |

| callsv                       | ml_sinf4_ha     | #36.3 | # LOE rbx r12 r13 r14 r15 xmm0 xmm8 xmm9 |  |  |

Copyright © 2014, Intel Corporation. All rights reserved. \*Other names and brands may be claimed as the property of others.

Optimization Notice

### Prototype Implementation

#### **Before Vectorization:**

%call = call float @sinf(float %div) #4, !dbg !22

Adding a Clang FE patch would be something like: %call = call float @llvm.sin.f32(float %div) #4, !dbg !22

#### After Vectorization:

%4 = call <4 x float> @llvm.sin.v4f32(<4 x float> %3), !dbg !27, !imf-precision !10, !imf-max-error !11

!10 = !{!"imf-precision=high"}

!11 = !{!"imf-max-error=0.6"}

#### After SVML translation pass:

%3 = call <4 x float> @\_\_svml\_sinf4\_ha(<4 x float> %2)

### Prototype Implementation with XMM

```

vector.body:

; preds = %vector.body, %entry

%index = phi i64 [ 0, %entry ], [ %index.next, %vector.body ], !dbg !2

%0 = trunc i64 % index to i32, !dbg !7

%broadcast.splatinsert6 = insertelement <8 x i32> undef, i32 %0, i32 0, !dbg !7

%broadcast.splat7 = shufflevector <8 x i32> %broadcast.splatinsert6, <8 x i32> undef, <8 x i32> zeroinitializer, !dbg

!7

%induction8 = add <8 x i32> %broadcast.splat7, <i32 0, i32 1, i32 2, i32 3, i32 4, i32 5, i32 6, i32 7>, !dbg !7

\%1 = \text{sitofp} < 8 \times i32 > \% induction 8 to < 8 \times \text{float} >, !dbg !7

%shuffle = shufflevector <8 x float> %1, <8 x float> undef, <4 x i32> <i32 0, i32 1, i32 2, i32 3>

%vcall = call <4 x float> @__svml_sinf4_ha(<4 x float> %shuffle)

%shuffle.1 = shufflevector <8 x float> %1, <8 x float> undef, <4 x i32> <i32 4, i32 5, i32 6, i32 7>

%vcall.2 = call <4 x float> @ svml sinf4 ha(<4 x float> %shuffle.1)

%shufflecomb = shufflevector <4 x float> %vcall, <4 x float> %vcall.2, <8 x i32> <i32 0, i32 1, i32 2, i32 3, i32 4,

i32 5, i32 6, i32 7>

%2 = getelementptr inbounds float, float* %array, i64 %index, !dbg !8

%3 = bitcast float* %2 to <8 x float>*, !dbg !9

#pragma omp simd simdlen(8)

store <8 x float> %shufflecomb, <8 x float>* %3, align 4, !dbg !9, !tbaa !10

for (i = 0; i < 1000; i++)

%index.next = add i64 %index, 8, !dbg !2

array[i] = sinf(i);

%4 = icmp eq i64 %index.next, 1000, !dbg !2

br i1 %4, label %for.end, label %vector.body, !dbg !2, !llvm.loop !14

}

```

### Summary

- ✓ OpenMP is evolving with a set of new features that needs scalar optimization, vectorization and loop optimizations to be seamlessly integrated with parallelization (privatization, lowering, outlining, ... etc.)

- ✓ Multiple languages support with effective engineering and maintaining cost

- $\checkmark$  Path-finding efforts to study feasibility of the Back-End solution

- Minimal extensions for LLVM IR

- $\checkmark$  Minimal Impact on LLVM infrastructure and optimizations

- ✓ Getting optimal threaded code to leverage target HW potential

- ✓ Targeting modern CPUs, Coprocessors, GPUs, DSP, FPGA, ... etc.

# Thanks & Questions?

Copyright © 2014, Intel Corporation. All rights reserved. \*Other names and brands may be claimed as the property of others.

Optimization Notice

### Legal Disclaimer & Optimization Notice

INFORMATION IN THIS DOCUMENT IS PROVIDED "AS IS". NO LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. INTEL ASSUMES NO LIABILITY WHATSOEVER AND INTEL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY, RELATING TO THIS INFORMATION INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

Software and workloads used in performance tests may have been optimized for performance only on Intel microprocessors. Performance tests, such as SYSmark and MobileMark, are measured using specific computer systems, components, software, operations and functions. Any change to any of those factors may cause the results to vary. You should consult other information and performance tests to assist you in fully evaluating your contemplated purchases, including the performance of that product when combined with other products.

Copyright © 2014, Intel Corporation. All rights reserved. Intel, Pentium, Xeon, Xeon Phi, Core, VTune, Cilk, and the Intel logo are trademarks of Intel Corporation in the U.S. and other countries.

#### **Optimization Notice**

Intel's compilers may or may not optimize to the same degree for non-Intel microprocessors for optimizations that are not unique to Intel microprocessors. These optimizations include SSE2, SSE3, and SSSE3 instruction sets and other optimizations. Intel does not guarantee the availability, functionality, or effectiveness of any optimization on microprocessors not manufactured by Intel. Microprocessor-dependent optimizations in this product are intended for use with Intel microprocessors. Certain optimizations not specific to Intel microarchitecture are reserved for Intel microprocessors. Please refer to the applicable product User and Reference Guides for more information regarding the specific instruction sets covered by this notice.

Notice revision #20110804

(intel)

30